Transceiver CW 20 m – VFO – Partie 4

Amplificateur du VFO

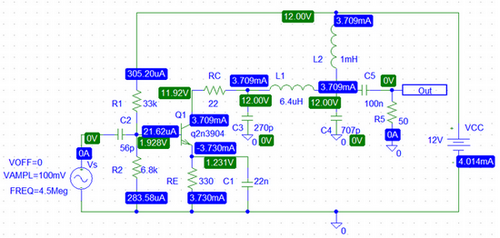

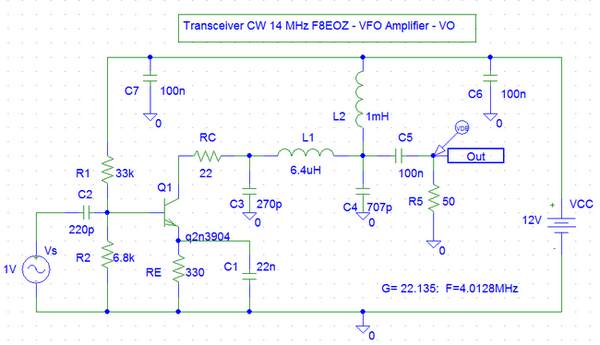

Rien que de classique dans cet amplificateur à émetteur commun. Polarisation par pont de base, résistance d’émetteur pour stabiliser le point de repos, sortie sur le collecteur chargé par le filtre passe-bas décrit en partie 3 avec adaptation d’impédance.

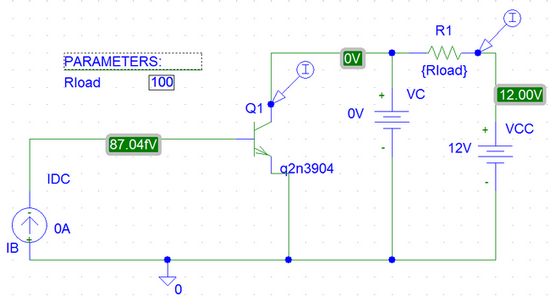

Ce montage est l’occasion de tester PSpice, un outil de simulation disponible sur internet.

Pour l’étudier et simuler son fonctionnement j’ai choisi d’utiliser PSpice 9.1 Student version. Voir note d’installation ci-dessous.

Polarisation du transistor

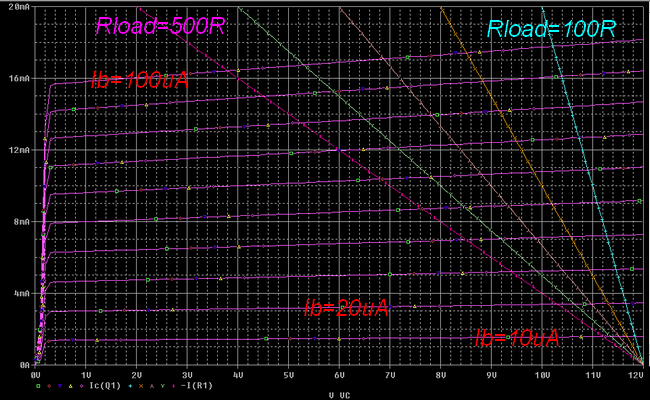

Avec le schéma du circuit Fig. 1, ci-dessous, il est facile avec Pspice de tracer le réseau des caractéristiques de sortie du transistor, la droite de charge (load line) et de déterminer le point de repos (quiescent point ou Q-point). Les 2 sondes de courant, l’une sur le collecteur, l’autre sur la résistance de charge servent au tracé du réseau. Dans Analyse Setup, choisir DC Sweep avec l’option Nested DC Sweep, choisir aussi Parametric pour analyser l’effet de multiples valeurs du paramètre global Rload.

Le réseau obtenu est représenté Fig. 2 ci-dessous. Il est tracé dans la plage des valeurs des courants Ic et Ib qui nous intéressent. On observe la rotation de la droite de charge en fonction de la valeur de la résistance de charge Rload dont le centre de rotation est le point de Cutoff . Le courant de base Ib varie de 10uA à 100uA par pas de 10uA. Rload varie de 100 ohms à 500 ohms par pas de 100 ohms.

Détermination de β à partir du graphique

βAC = ∆IC /∆IB = (5,3 mA – 3,4 mA) / (30 uA – 20 uA) = 1,9 mA / 10 uA = 190 à VCE = 10 V

βDC = IC / IB = 3,4 mA / 20 uA = 170 à VCE= 10 V

Télécharger les fichiers PSpice du réseau de caractéristiques de sortie.

Simulation Bias Point Detail

Calcul du courant de base IB et du courant de collecteur IC

Données :

VCC = 12 V

ß typique = 150

RE = 330 Ω RC = 22 Ω R1 = 33 KΩ R2 = 6,8 KΩ

IC0 courant de collecteur de polarisation.

IB0 courant de base de polarisation.

Hypothèse à vérifier : le courant dans le pont de base R1 et R2 est >> IB0.

Calcul:

Le gain en courant ß du transistor est >> 1, en admettant que :

IC = IE . β / (1 + β) ≈ IE il vient, IC0 = VE0 / RE = IE.

De ce fait le gain β n’intervient plus dans les formules suivantes.

IE = (1 / RE ) . [VCC .( R2 / (R1 + R2)) - Uj] = ( 1 / 0,33) . [ 12 . (6,8 / (33 + 6,8)) - 0,7] = 4,1 mA,

avec Uj = 0,7 V (jonction BE),

IC0 = IE = 4,1 mA.

On vérifie que le courant dans le pont de base VCC / (R1 + R2) = 12 / (33 + 6,8 ) = 302 μA est bien >> IB0 = IC0 / β = 27 μA ( courant dans le pont de base > 10 IB0 ).

On en déduit :

VE0 = RE . IE0 = 0,330 . 4,1 = 1,35 V,

VC0 = VCC – RC . IC0 = 12 – 0,022 . 4,1 = 11,91 V,

VCE0 = VC0 – VE0 = 11,91 – 1,35 = 10,56 V.

Avec quelques clics, la simulation Fig. 3 permet de connaître les tensions et courants de tous les noeuds du circuit calculés avec les formules précédentes. On vérifie :

IB0 = 21,62 uA ≈ 27 uA calculé,

IE = 3,73 mA ≈ 4,1 mA calculé,

VE0 = 1,231 V ≈ 1,35 V calculé,

VC0 = 11,92 V ≈ 11,91 V calculé,

VCE0 = VC0 – VE0= 11,92 – 1,231 = 10,689 V ≈ 10,56 V calculé.

Je continue l’étude de PSpice appliquée à l’analyse de l’amplificateur du VFO.

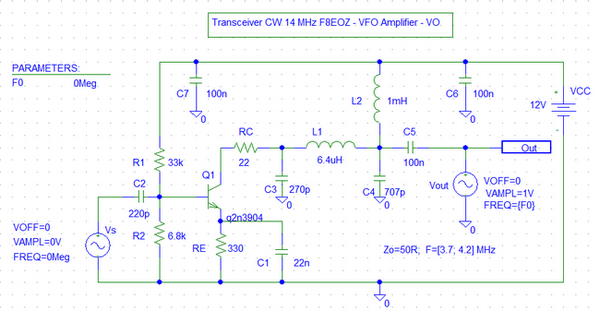

Analyse de l’impédance de sortie

Le circuit Fig. 4 est examiné avec l’analyse Transient (domaine du temps) avec les paramètres suivants:

Print Step = 0.1ms

Final Time = 200ms

No-Print Delay = 150ms.

Je crée un paramètre global F0 qui désigne la fréquence du générateur Vout.

J’utilise la fonction Parametric de Analysis Setup avec les paramètres suivants:

Swept Var. Type = Global Parameter

Sweep Type = Linear

Name = F0

Start Value = 3.7Meg

End Value = 4.2 Meg

Increment = 0.1Meg.

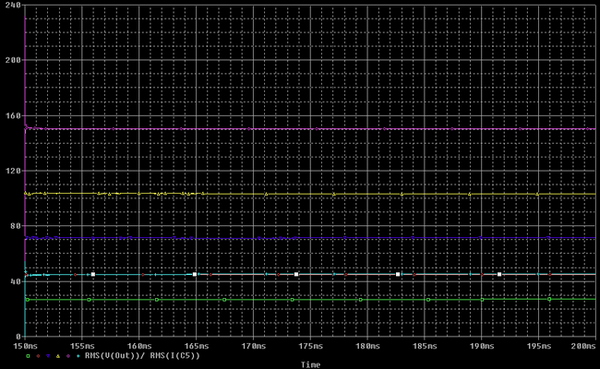

J’affiche l’expression RMS(V(Vout))/RMS(I(C5)), qui représente l’impédance de sortie du circuit.

Le graphe obtenu Fig. 5 montre que l’impédance de sortie Zo dans la plage de fréquences, varie de 27 à 150 ohms:

| Fréquence MHz | Impédance Zo ohms |

|---|---|

| 3.7 | 27 |

| 3.8 | 46 |

| 3.9 | 71 |

| 4.0 | 103 |

| 4.1 | 150 |

| 4.2 | 46 |

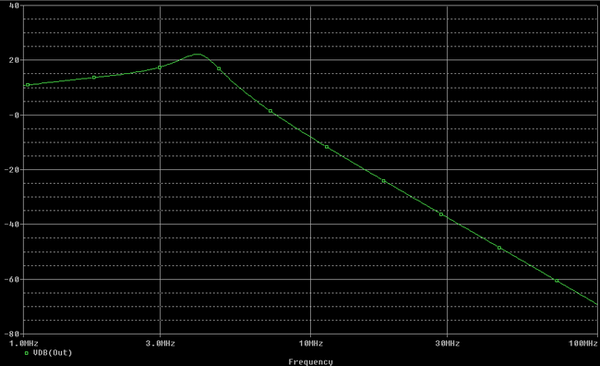

Analyse de la réponse en fréquence

Le circuit Fig. 6 est examiné avec l’analyse AC Sweep (domaine des fréquences) avec les paramètres suivants:

AC Sweep Type = Decade

Pts/Decade = 100

Start Freq. = 1 Meg

End Freq. = 100Meg

Le diagramme de Bode obtenu Fig. 7 montre que le gain maximum G = 22,135 est obtenu à la fréquence F = 4,0128 MHz.

Télécharger les fichiers PSpice de simulation.

Réalisation

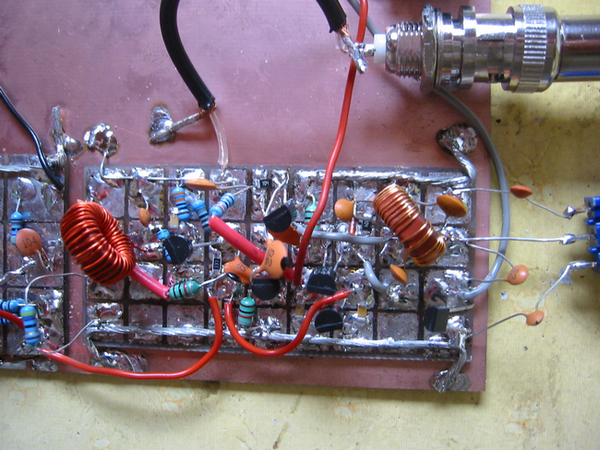

Le circuit est réalisé sur une plaque d’époxy cuivrée simple face de 7 x 3,2 cm.

Pour dessiner le circuit, j’utilise 2 feutres fins de la marque STABILO feutre OHPen universal pour films transparents, noir F, permanent, largeur de tracé: 0,7 mm, et S largeur de tracé: 0,4 mm. Pour noircir les surfaces j’utilise un feutre large noir permanent CIF.

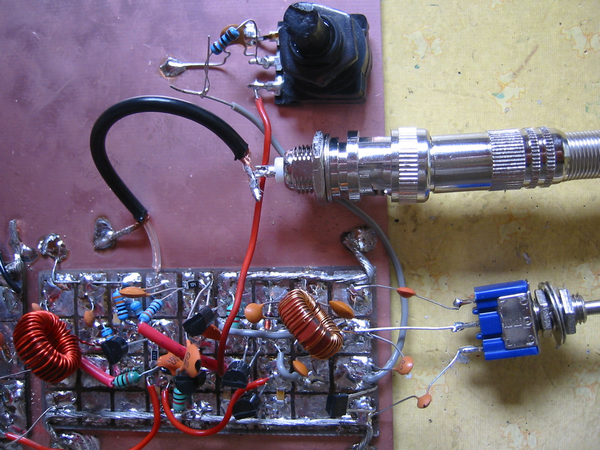

La gravure est simple: 9 x 4 = 36 îlots identiques. Un îlot a été divisé en 2 parties identiques pour souder le transistor de l’amplificateur du fréquencemètre. Chaque îlot est séparé de 0,5 mm pour permettre de placer éventuellement des composants CMS 1206 ou 0805. En effet, le circuit est dense. Pour réduire les connexions j’ai utilisé chaque fois que possible ces composants minuscules qui se soudent très facilement en utilisant la technique décrite par Francis THOBOIS. Cette plaque est soudée au moyen du fil de masse sur la plaque d’époxy cuivrée qui sert de support à toutes les cartes. La photo 1 montre le circuit en gros plan. On y distingue les CMS. La photo 2 montre le circuit en test avec le potentiomètre, l’inverseur, le connecteur BNC vers le fréquencemètre, la résistance de charge de 47 ohms soudés provisoirement. Le circuit sera ensuite entouré d’un blindage d’époxy cuivré.

![]()

Photo 2

Test

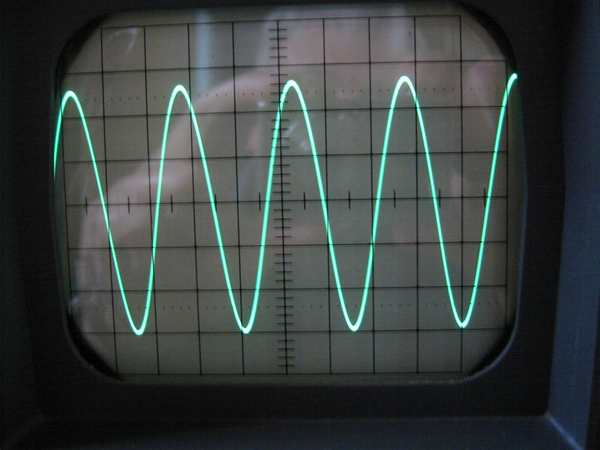

Résistance de charge connectée en sortie du VFO = 47 ohms ≈ 50 ohms.

Fréquence de mesure F = 4MHz.

Après un temps de chauffage de 15 mn pour assurer la stabilité de l’oscillateur,

avec la sonde 1:1 à l’échelle 0,5V/cm, l’oscilloscope donne Vpp = 2,9V.

Pour la mesure HF, j’utilise aussi une sonde HF sur le modèle N5ESE’s Ballpoint RF Probe. La sonde donne sur le multimètre Vrms = 1,132 V soit Vpp = 1,132*2*√2 = 3,2 V valeur voisine de celle lue sur l’oscilloscope.

Calcul de la puissance de sortie Po sur 50 ohms:

Po = 1.132 * 1.132 / 50 = 26 mW soit 10 log 26 = 14dBm.

En faisant varier la fréquence d’un bout à l’autre de la gamme, la sonde HF indique Vrms = [0,970; 1,170] V

Comme on le constate sur la photo 3, le signal en sortie est net.

Photo 3 signal de sortie du VFO

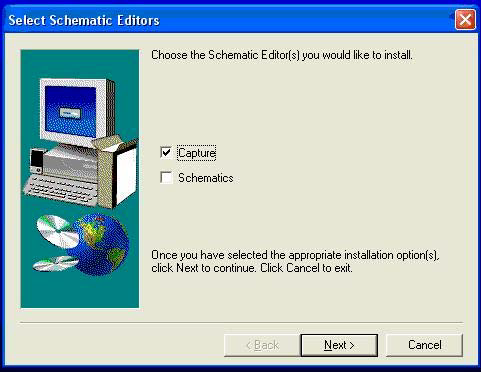

Installer PSpice 9.1 Student version

PSpice permet de concevoir et de simuler des circuits analogiques et numériques. Student version est une version libre, allégée mais qui, pour l’amateur et l’étudiant est tout à fait adaptée à la simulation et à la compréhension du fonctionnement des circuits électroniques. Je l’ai installée sur W7 64 bits. Son installation est très rapide et sans soucis si vous suivez la procédure suivante:

1) Télécharger PSpice ici

2) Décompressez le ficier zip dans un répertoire temporaire

3) Dans ce répertoire exécuter Setup.exe

4) Très important: cochez l’option Schematics, sinon il vous sera impossible d’exécuter la simulation.

Le logiciel est installé dans le répertoire Programmes/ORCAD_Demo.

Pour l’exécuter cliquer sur le manager …/PSpice/appmgr.exe. Là, créez un workspace d’où il est possible de lancer l’éditeur de schémas et la simulation.

Dans l’éditeur de schémas, si cela n’est pas fait, indiquez les bibliothèques de composants. Pour cela, aller dans Option>Editor Configuration bouton Library Settings, sélectionner:

abm .slb

analog.slb ,analog .plb

analog_p.slb

breakout .slb

eval.slb , eval.plb

port .slb

source.slb

sourcstm.slb

special.slb .

Tous ces paramètres sont stockés dans le fichier PSPICEEV.INI. Ce fichier n’est pas placé dans le répertoire du logiciel ORCAD_Demo mais dans un répertoire du système d’exploitation. Pour le trouver, faire une recherche avec l’explorateur Windows. Si, comme moi, vous le modifiez, faire d’abord une copie de sauvegarde et vous donner les droits de le modifier. J’ai été conduit à le modifier pour réparer 2 erreurs:

dans l’éditeur de schémas « undefined format layout choosen: pcboard »

dans examine netlist « out of memory »

J’ai modifié la section [SCHEMATICS INTERFACES]. En cas de problème téléchargez mon fichier PSPICEEV.INI, vérifiez chaque section.

Références : PSpice help contient la description des paramètres de PSPICEEV.INI

Il existe de nombreux tutoriels. Have fun!

Index des articles de la catégorie Transceiver

- Transceiver CW 20 m

- Transceiver CW 20 m – Amplificateur audio

- Transceiver CW 20 m – Amplificateur audio V2

- Transceiver CW 20 m – Amplificateur de puissance RF power amplifier

- Transceiver CW 20 m – Amplificateur IF CASCODE

- Transceiver CW 20 m – Amplificateur post-mélangeur

- Transceiver CW 20 m – Atténuateur en pi

- Transceiver CW 20 m – BFO

- Transceiver CW 20 m – Commutation Rx/Tx Switching

- Transceiver CW 20 m – Détecteur de produit

- Transceiver CW 20 m – Emetteur

- Transceiver CW 20 m – Filtre à quartz – Crystal ladder filter

- Transceiver CW 20 m – Filtre de sortie du PA

- Transceiver CW 20 m – Mélangeur – Double Balanced Mixer

- Transceiver CW 20 m – Module RF Version 2

- Transceiver CW 20 m – Oscillateur à réseau déphaseur RC phase shift oscillator

- Transceiver CW 20 m – Oscillateur et Mélangeur de l’émetteur

- Transceiver CW 20 m – PA Driver

- Transceiver CW 20 m – Récepteur – Amplificateur RF

- Transceiver CW 20 m – Récepteur – Filtre passe bande 14 MHz

- Transceiver CW 20 m – VFO – Partie 1

- Transceiver CW 20 m – VFO – Partie 2

- Transceiver CW 20 m – VFO – Partie 3

- Transceiver CW 20 m – VFO – Partie 4

- Transceiver CW 20 m – VFO V3

- Transceiver CW 20 m – VFO Version 2 – Etalement de la bande

[...] VFO – Partie 1 Transceiver CW 20 m – VFO – Partie 2 Transceiver CW 20 m – VFO – Partie 3 Transceiver CW 20 m – VFO – Partie 4 Transceiver CW 20 m – Mélangeur – Double Balanced Mixer Transceiver CW 20 m – Atténuateur [...]